A/D-D/A Converter Circuit

Index 13

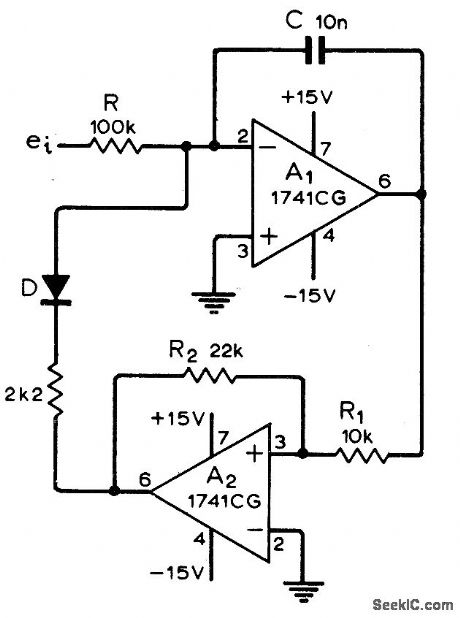

VOLTAGE_FREQUENCY_CONVERTER

Published:2009/7/6 7:01:00 Author:May

Uses opamp A1 as integrator and A2 as regenerative comparator with hysteresis, to generate sequence of pulses with repetition frequency proportional to DC input voltage, Article gives design equations and typical waveforms. Input voltage range is 10 mV to 20 V for linear operation.-G. B. Clayton, Experiments with Operational Amplifiers, Wireless World, Dec. 1973, p 582. (View)

View full Circuit Diagram | Comments | Reading(0)

RESOLVER

Published:2009/7/6 5:14:00 Author:May

Circutt accepts DC input voltages R and X and generates two DC output voltages R sin X and R cos X. Can be used in guidance computers to solve coordinate conversion problems (polay to rectangular) and in feedback systems to convert rectangular to polar coordinate. Sine wave is generater by chopping input signalR and filtering resulting square wave. Sine wave is then samlpled at time controlled by X to generate R sin X. Cosine output is obtained by shifting first output 90oinphase.Circuit also generates proper sampling pulses and contains two sample-and-hold circuits on outPuts-W. H. Licata, Solid-State Resolver, EDN Magaz,ne, July 20, 1973, p 82-83. (View)

View full Circuit Diagram | Comments | Reading(1632)

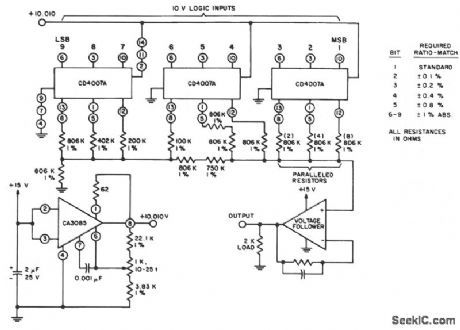

9_BIT_CMOS_D_A_CONVERTER

Published:2009/7/6 3:30:00 Author:May

Three CD4007A IC packages perform the switch function using a 10-V logic level. A single 15-V supply provides a positive bus for the follower amplifier and feeds the CA3085 voltage regulator. The scale adjust function is prodded by the regulator output control, which is set to a nominal 10 V in this system. The line-voltage regulation (approximately 0.2%) permits 9-bit accuracy to be maintained with a variation of several volts in the supply. System power consumption ranges between 70 and 200 mW; a major portion is dissipated in the load resistor and op amp. The regulated supply provides a maximum current of 440 μA of which 370 μA flows through the scale adjusting. The resistor ladder is composed of 1% tolerance metaloxide film resistors. The ratio match between resistance values is in the order of 2%. The follower amplifier has the offset adjustment nulled at approximately a 1 V output level. (View)

View full Circuit Diagram | Comments | Reading(969)

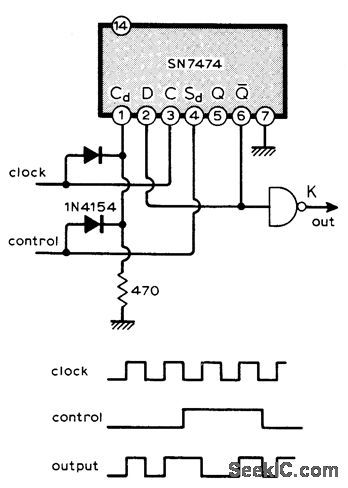

SWITCHED_DIVIDER_FOR_BINARY_COUNTER

Published:2009/7/6 3:29:00 Author:May

Simple circuit provides method of switching division by two into or out of stream of clock pulses. Output is in phase with input and free of spikes. Switching requires only one D-type flip-flop and one inverter. When control is high, logic action gives normal connection for division by two,using D-typeflip-flop; inverterthen restores phase.-J. M. Firth, Control of a Binary Counter for Division by One or Two, Wireless World, Jan. 1975, p 12.

(View)

View full Circuit Diagram | Comments | Reading(1075)

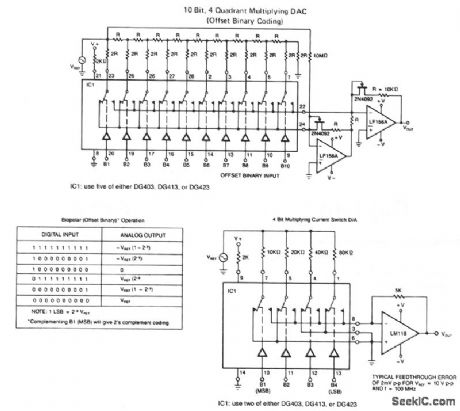

DIGITAL-TO_ANALOG_CONVERTERS

Published:2009/7/6 3:07:00 Author:May

The following applications circuits are intended to illustrate the following points

.A 2-KΩ resistor should be in series with V+ to limit supply current with negative ringing of the bit inputs

.Temperature compensation for RDs(on) can be provided in the feedback path of the op amp

.Bipolar reference voltages can be used in all configurations (View)

View full Circuit Diagram | Comments | Reading(1099)

8_bit_D_A_converter_with_microprocessor_interface_1

Published:2009/7/23 21:46:00 Author:Jessie

This circuit uses a DAC-4888 and a few external components to form a D/A converter with microprocessor interface (8-bit data bus). The output is 0 to -4 mA with straight binary input and an external reference. (View)

View full Circuit Diagram | Comments | Reading(946)

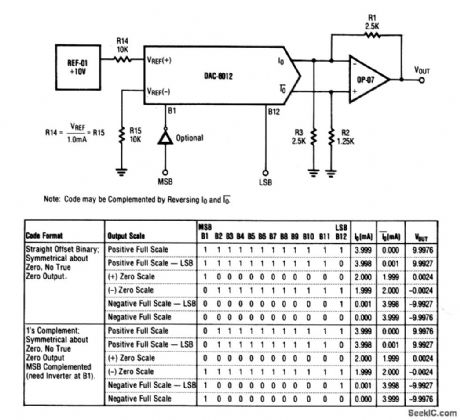

Symmetrical_offset_D_A_converter

Published:2009/7/23 21:51:00 Author:Jessie

This circuit shows a DAC/op-amp combination that is used to provide symmetrical-offset operation. Full-scale adjustment can be made as shown in Fig.6-39B. (View)

View full Circuit Diagram | Comments | Reading(792)

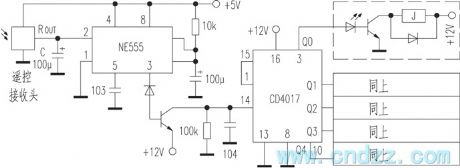

The remote control signal input switching circuit

Published:2011/7/31 22:54:00 Author:Christina | Keyword: remote control, signal, input switching

The digital audio decoder needs a five-choose-one switch to switch three groups of coaxial BS, CD, DAT and two groups of optical signal input. In order to make the digital audio decoder panel concise, we design this kind of switching circuit. This circuit is as shown in the figure.

In this figure, the receiving head receives the remote control pulse signal, and it forms the steep falling pulse edge through the capacitor C to trigger the monostable flip which is composed of the NE555, then the counter CD4017 starts counting, the Q port of it increases one bit, the corresponding relay operats to switch the corresponding input signal. The CD4017 only uses five Q ports, so the pins of it need to connect with each other.

(View)

View full Circuit Diagram | Comments | Reading(1006)

ANALOG_DIGITAL_CONVERSION

Published:2009/7/5 22:09:00 Author:May

Circuit canbe used for either ramp orsuccessive-approximation method of converting analog input to digital word, applying it to DAC, and comparing analog output of DAC to analog input to be converted. Results of comparison determine next digital word to be generated for DAC by microprocessor. LM301A changes 0-2 mA output of DAC into 0-5 V for LM311 comparator. To calibrate, apply all 0s to DAC; pin 6 of LM301A should now be near 0V Apply all 1s to DAC and adjust output of LM301A to 5.00 V with R4,Conversion routines implementing these functions are given for Motorola MC6800 and Intel 8008 microprocessors.-R, Frank, Microprocessor Based Analog/Digital Conversion.BYTE, May 1976.p70-73. (View)

View full Circuit Diagram | Comments | Reading(1954)

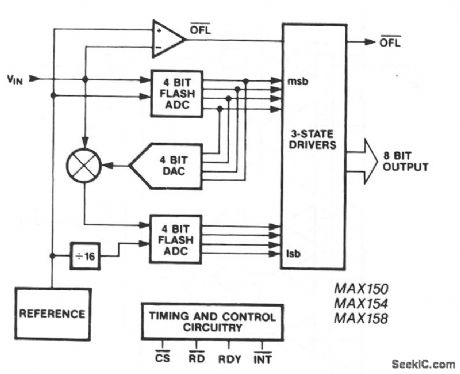

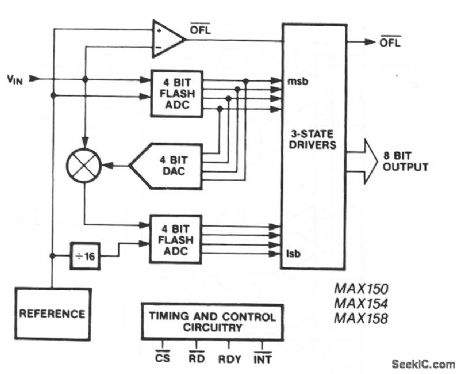

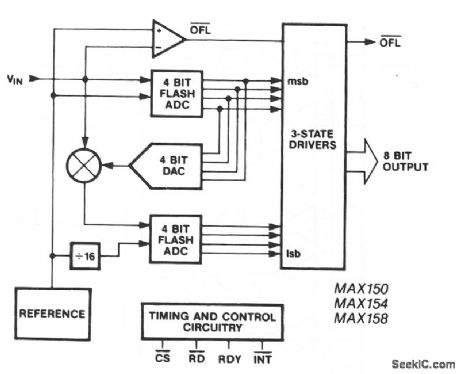

HALF_FLASH_ADC

Published:2009/7/5 21:17:00 Author:May

An a/d conversion technique which combines some of the speed advantages of flash conversion with the circuitry savings of successive approximation is termed half-flash. In an 8-bit, half-flash converter, two 4-bit flash a/d sections are combined. The upper flash a/d compares the input signal to the reference and generates the upper 4 data bits. This data goes to an internal DAC, whose output is subtracted from the analog input. Then, the difference can be measured by the second flash a/d, which provides the lower 4 data bits. (View)

View full Circuit Diagram | Comments | Reading(2604)

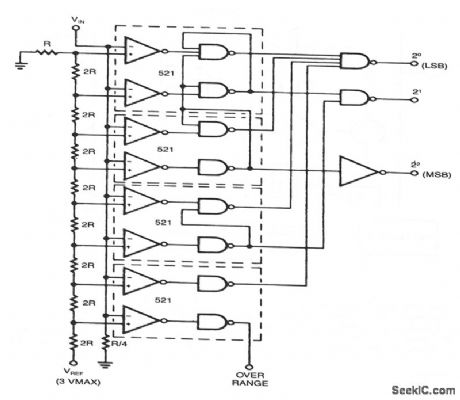

ADC

Published:2009/7/5 21:10:00 Author:May

Conversion speed of this design is the sum of the delay through the comparator and the decoding gates. Reference voltages for each bit are developed from a precision resistor ladder network. Values of R and 2R are chosen so that the threshold is 1/2 of the least significant bit. This assures maximum accuracy of ±1/2 bit. The individual strobe line and duality features of the NE521 greatly reduced the cost and complexity of the design. (View)

View full Circuit Diagram | Comments | Reading(2897)

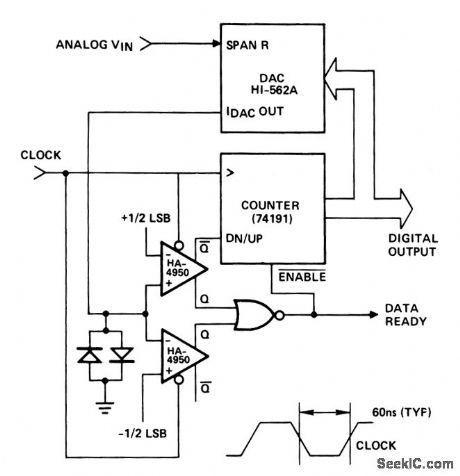

TRACKING_ADC

Published:2009/7/5 21:08:00 Author:May

The analog input is fed into the span resistor of a DAC .he analog input voltage range is selectable in the same way as the output voltage range of the DAC.The net current flow through the ladder termination resistance;i.e.,2 KΩ for HI-562A; produces an error voltage at the DAC output.This error voltage is compared with 1/2 LSB by a comparator. When the error voltage IS within±1/2 LSB range,the Q output ofthe comparators are both low,which Stops the counter and gives a data ready signal to indicate that the digital output is correct,If the error exceeds the±1/2 LSB range,the counter iS enabled and driven In anup or down direction depending on the polarity of the error voltage.

The digital output changes state only when there is a significant change in the analog input.When monitoring a slowly varying input,it is necessary to read the digital output only after a change has taken place.The data ready signal could be used to tngger a flip-flop to indicate the condition and reset it after readout.The main disadvantage of the tracking ADC iS the time required to initially acqutre a signal;for a 12-bit ADC,it could be up to 4096 clock periods.The input signal usually must be filtered so that its rate of change does not exceed the tracking range of the ADC—1 LSB per clock period.

(View)

View full Circuit Diagram | Comments | Reading(2004)

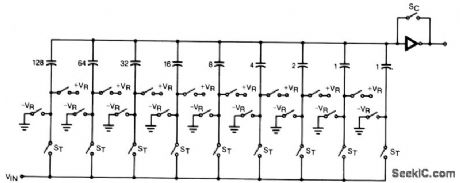

SWITCHED_CAPACITOR_ADC

Published:2009/7/5 20:57:00 Author:May

The CMOS comparator in the successive-approximation system determines each bit by examining the charge on a series of binary-weighted capacitors. In the first phase of the conversion process, the analog input is sampled by closing switch SC and all ST switches, and by simultaneously charging all the capacitors to the input voltage.

In the next phase of the conversion process, all ST and SC switches are opened and the comparator begins identifying bits by identifying the charge on each capacitor relative to the reference voltage. In the switching sequence, all 8 capacitors are examined separately until all 8 bits are identified, and then the charge-convert sequence is repeated. In the first step of the conversion phase, the comparator looks at the first capacitor (binary weight = 128). One pole of the capacitor is switched to the reference voltage, and the equivalent poles of all the other capacitors on the ladder are switched to ground. If the voltage at the summing node is greater than the trip point of the comparator-approximately 1/2 the reference voltage, a bit is placed in the output register, and the 128-weight capacitor is switched to ground. If the voltage at the summing node is less than the trip point of the comparator, this 128-weight capacitor remains connected to the reference input through the remainder of the capacitor-sampling (bit-counting) process. The process is repeated for the 64-weight capacitor, the 32-weight capacitor, and so forth down the line, until all bits are tested. With each step of the capacitor-sampling process, the initial charge is redistributed among the capacitors. The conversion process is successive-approximation, but relies on charge shifting rather than a successive-approximation register-and reference d/a-to count and weigh the bits from MSB to LSB.

(View)

View full Circuit Diagram | Comments | Reading(1283)

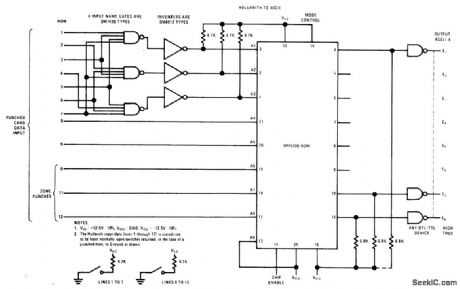

CARD_CONVERTER

Published:2009/7/3 5:03:00 Author:May

National MM530B ROM forms basis for conversion of 12-line Hollerith punched-card code to 8-line ASCll. All 12 inputs from cards are presented to programmable logic array (PLA). Invalid input produces all-high output state because it is not recognizable product term. First 7 Hollerith lines, which are ordinary decimally coded lines, are encoded to 3 binary lines with additional logic elements shown, before being presented into common 8-input ROM.- Memory Databook, National Semiconductor, Santa Clara, CA, 1977, p 11-49-11-56. (View)

View full Circuit Diagram | Comments | Reading(1361)

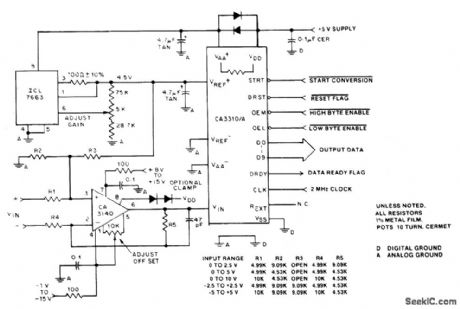

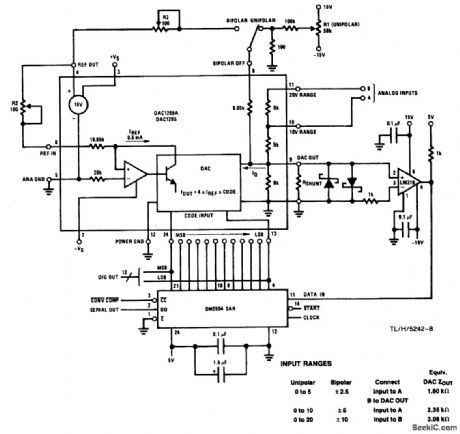

DIFFERENTIAL_INPUT_A_D_SYSTEM

Published:2009/7/2 4:06:00 Author:May

Using a CA3140 BiMOS op amp provides good slewing capability for high bandwidth input signals, and can quickly settle energy that the CA3310 outputs at its VIN terminal. The CA3140 can also drive close to the negative supply rail. If system supply sequencing or an unknown input voltage is likely to cause the op amp to drive above the VDD supply, a diode clamp can be added from pin 8 of the op amp to the VDD supply. (View)

View full Circuit Diagram | Comments | Reading(1154)

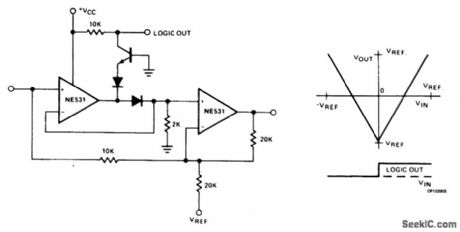

CYCLIC_A_D_CONVERTER

Published:2009/7/2 4:04:00 Author:May

The cydic converter consists of a chain of identical stages, each of which senses the polarity of the input. The stage then subtracts VREF from the input and doubles the remainder if the polarity was correct. The signal is full-wave rectifted and the remainder of VIN - VREF is doubled. A chain of these stages gives the gray code equivalent of the input voltage in digitized form related to the magnitude of VREF. Possessing high potential accuracy, the circuit using NE531 devices settles in 5 μs. (View)

View full Circuit Diagram | Comments | Reading(1026)

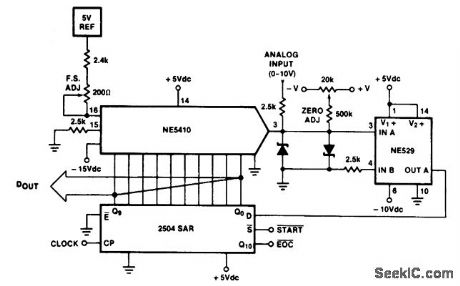

SUCCESSIVE_APPROXIMATION_A_D_CONVERTER_1

Published:2009/7/2 4:02:00 Author:May

The 10-bit conversion time is 3.3 μs with a 3 MHz clock. This converter uses a 2504 12-bit successive approximation register in the short cycle operating mode where the end of conversion signal is taken from the first unused bit of the SAR (Q10). (View)

View full Circuit Diagram | Comments | Reading(1139)

HIGH_SPEED_12_BIT_A_D_CONVERTER

Published:2009/7/2 4:00:00 Author:May

This system completes a full 12-bit conversion in 10 μs unipolar or bipolar. This converter will 6e accurate to ±1/2 LSB of 12 bits and have a typical gain TC of 10 ppm/℃. In the unipolar mode, the system range is 0 V to 9.9976 V, with each bit having a value of 2.44 mV. For the true conversion accuracy, an A/D converter should be trimmed so that given bit code output results from input levels from 1/2 LSB below to 1/2 LSB above the exact voltage which that code represents. Therefore, the converter zero point should be trimmed with an input voltage of 1.22 mV; trim R1 until the LSB just begins to appear in the output code (all other bits 0 ). For full-scale, use an input voltage of 9.9963 V (10 V-1 LSB-1/2 LSB); then trim R2 until the LSB just begins to appear (all other bits 1 ). The bipolar signal range is -5.0 V to 4.9976 V. Bipolar offset trimming is done by applying a -4.9988 V input signal and trimming R3 for the LSB transition (all other bits 0 ). Full-scale is set by applying 4.9963 V and trimming R2 for the LSB transition (all other bits 1 ). (View)

View full Circuit Diagram | Comments | Reading(1266)

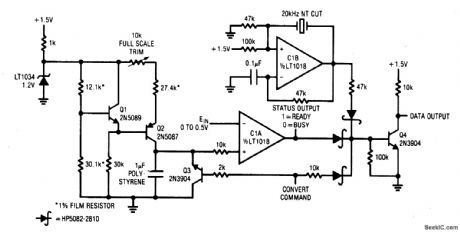

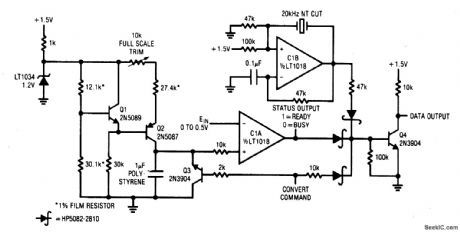

10-BIT_A_D_CONVERTER

Published:2009/7/2 3:56:00 Author:May

The converter has a 60 ms conversion time, consumes 460 μA from its 1.5 V supply and maintains 10 bit accuracy over a 15℃ to 35℃ temperature range. A pulse applied to the convert command line causes Q3, operating in inverted mode, to discharge through the 10 kΩ diode path, forcing its collector low. Q3's inverted mode switching results in a capacitor discharge within 1 mV of ground. During the time the ramps' value is below the input voltage, CIA's output is low. This allows pulses from C1B, a quartz stabilized oscillator, to modulate Q4. Output data appears at Q4's collector. When the ramp crosses the input voltages value C1A's output goes high, biasing Q4 and output data ceases. The number of pulses at the output is directly proportional to the input voltage. To calibrate apply 0.5 V to the input and trim the 10 kΩ potentiometer for exactly 1000 pulses out each time the convert command line is pulsed. (View)

View full Circuit Diagram | Comments | Reading(1204)

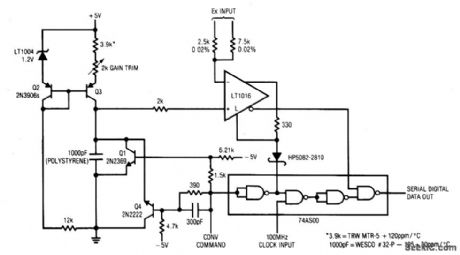

INEXPENSIVE,FAST_10_BIT_SERIAL_OUTPUT_A_D

Published:2009/7/2 3:53:00 Author:May

Everytime a pulse is applied to the convert command input, Q1 resets the 1000 pF capacitor to.0 V. This resetting action takes 200 ns of the falling edge of the convert command pulse, the capacitor begins to charge linearly. In precisely 10 microseconds, it charges to 2.5 V. The 10 microseconds ramp is applied to the LT1016's positive input. The LT1016 compares the ramp to Ex, the unknown, at its negative input. For a 0 V - 2.5 V range, Ex is applied to the 2.5 k ohm resistor. From a 0 V - 10 V range, the 2.5 k ohm resistor is grounded and Ex is applied to the 7.5 k ohm resistor. Output of the LT1016 is a pulse whose width is directly dependent on the value of Ex. This pulse width is used to gate a 100 MHz clock. The 100 MHz clock pulse bursts that appear at the output are proportional to Ex. For a 0 V - 10 V input, 1024 pulses appear at fullscale, 512 at 5.00 V, etc. (View)

View full Circuit Diagram | Comments | Reading(922)

| Pages:13/24 1234567891011121314151617181920Under 20 |

Circuit Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit